← Back to Students

Sara K.

Bio

Software and verification developer with hands-on experience in UVM, SystemVerilog, and C/C++. Skilled in building testbench components, developing algorithms, and implementing robust system logic in C++. Strong analytical mindset, fast learner, and eager to contribute to both verification and software engineering teams.

Skills

Verilog

SystemVerilog

UVM

Coverage

Assertions

Cadence Xcelium

Bootcamp Project

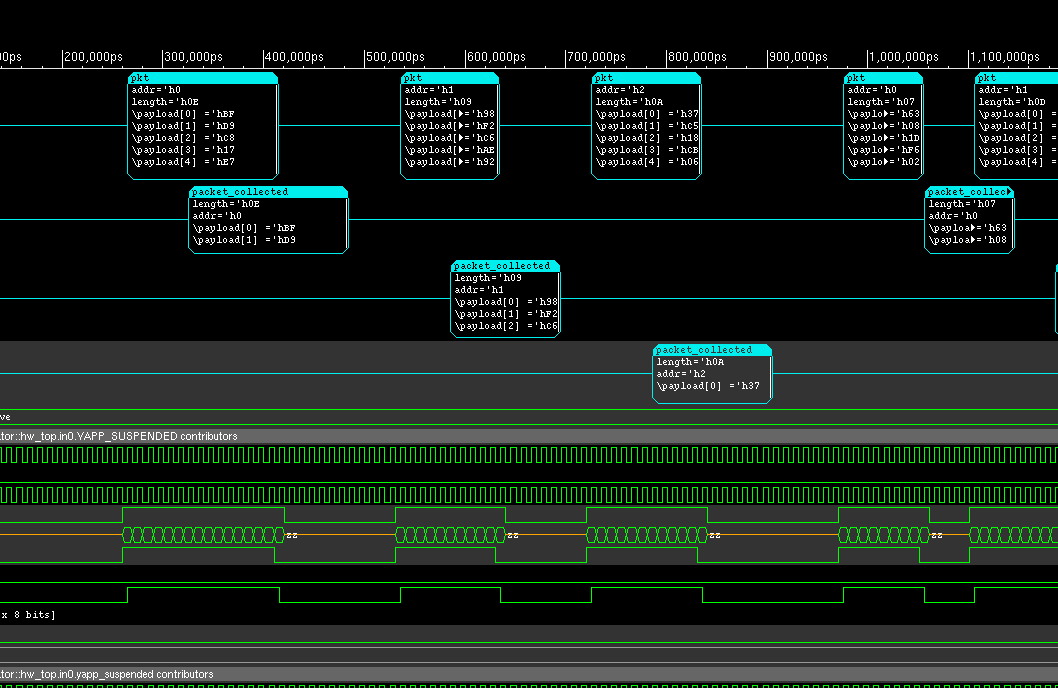

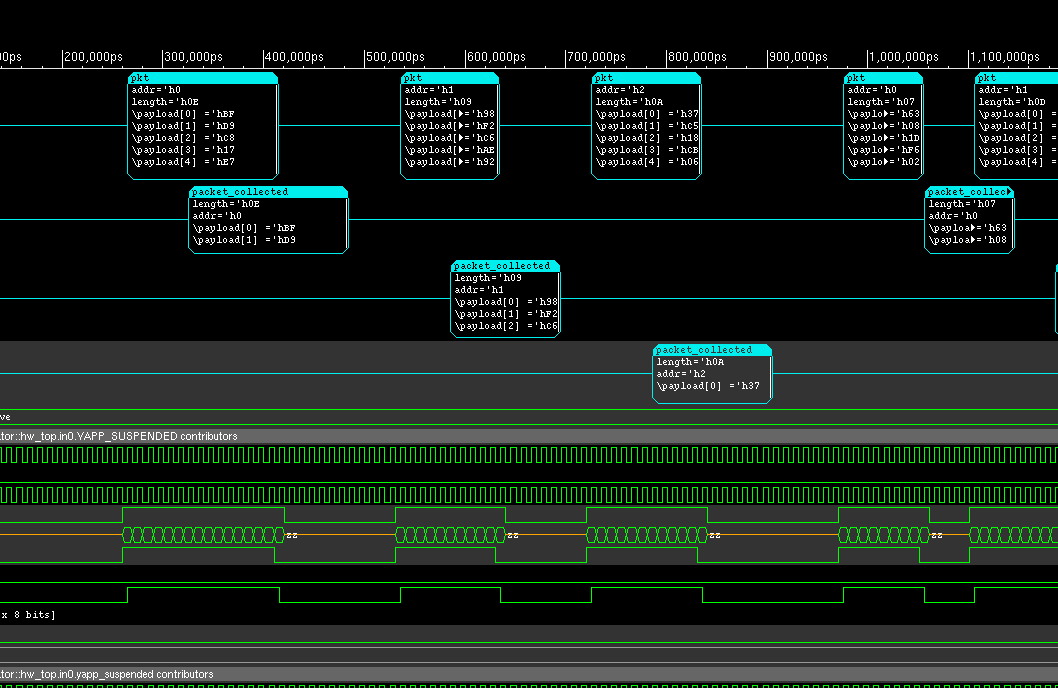

Complete UVM-based verification environment for a packet router

Mentored by: Qualcomm

Verification Bootcamp 2025 (Verification)

Responsibilities:

Executed full-system simulations, performed transaction tracing, analyzed waveform behavior, debugged constraints, and validated the correctness of the integrated verification environment.

Created the transaction-level stimulus model and implemented a sequence library generating constrained and protocol-accurate packet traffic.

Integrated all verification components with the DUT using virtual interfaces, including clock/reset logic, the YAPP input port, the HBUS interface, and output channels.

Combined multiple UVCs into a unified environment and coordinated multi-interface activity through a dedicated multichannel sequencer.

Implemented a TLM-based scoreboard that compares expected and actual packet routing across all DUT channels.

Developed a reference model that mirrors configuration settings and validates packet legality before forwarding them for end-to-end checking.

Performed full simulation runs, transaction tracing, and debugging to verify the correctness and stability of the integrated environment.

Click to enlarge

Additional Projects

End-to-end application combining an Angular client and a .NET Core REST API backend.

Client: task boards, CRUD operations, login, and admin dashboard.

Backend: JWT authentication, task management, per-user data isolation, and order processing.

English Level

Working Proficiency