← Back to Projects

Router Verification (UVM)

Mentored by: Qualcomm

Complete UVM-based verification environment for a packet router

SystemVerilog

UVM

RTL Verification

RAL

Scoreboard

Reference Model

Virtual Sequencer

Directed & Random Sequences

Description

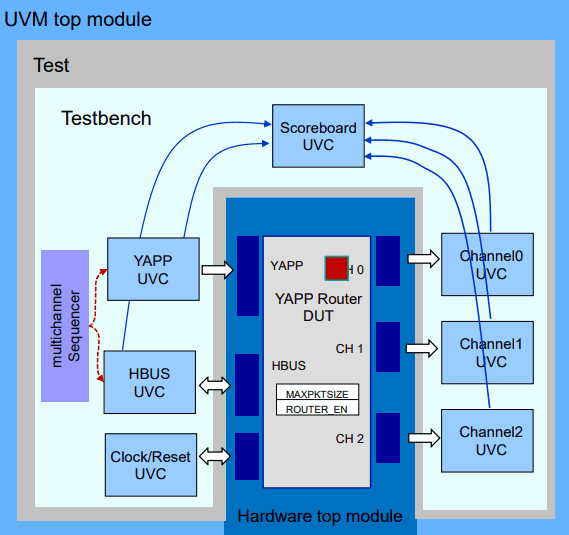

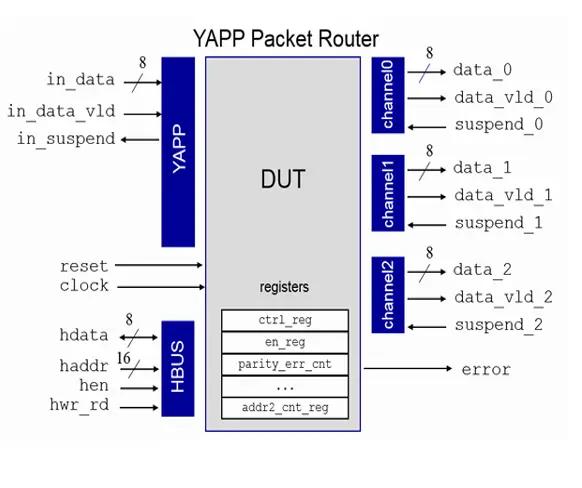

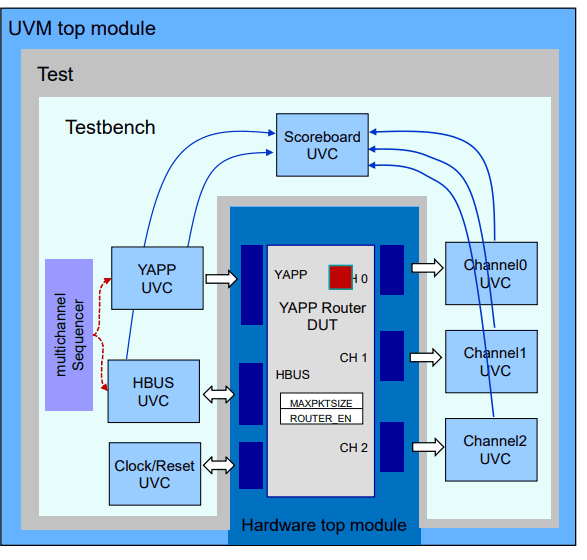

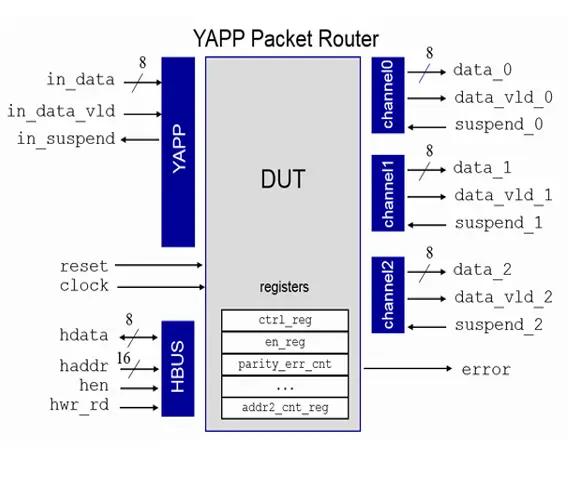

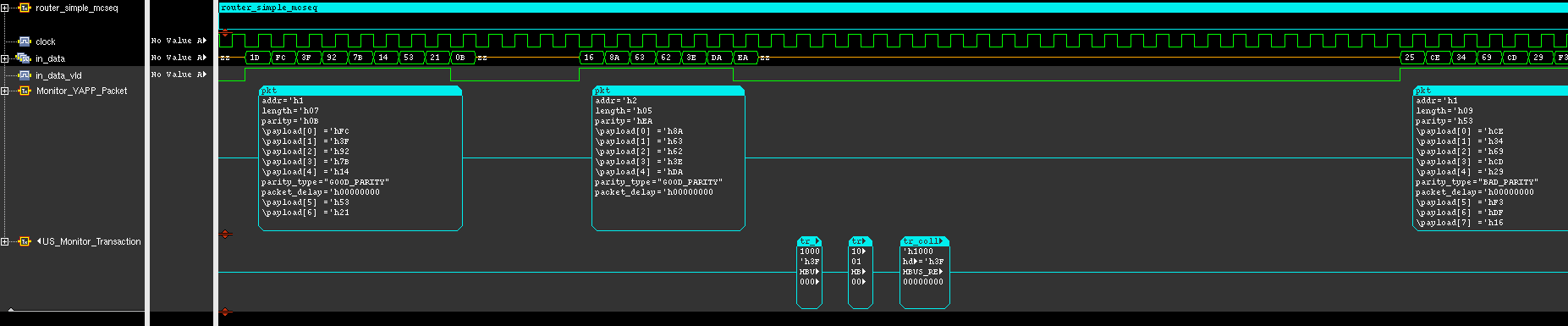

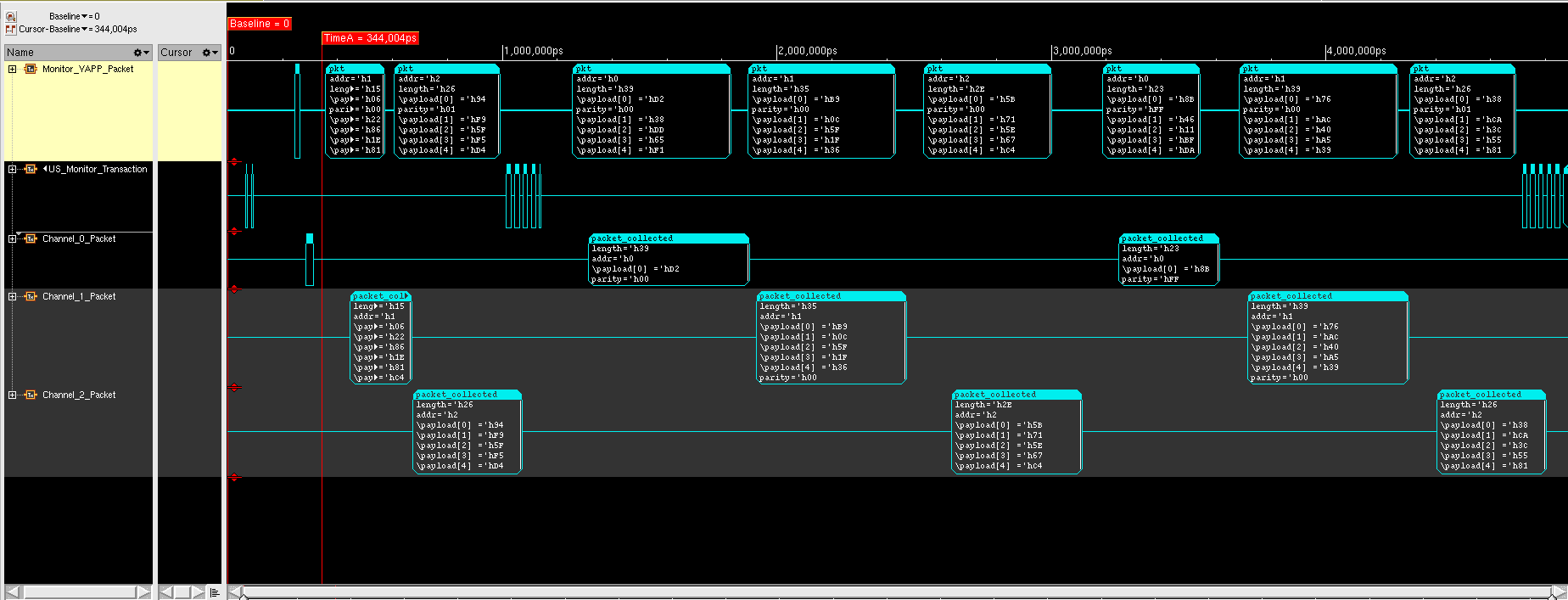

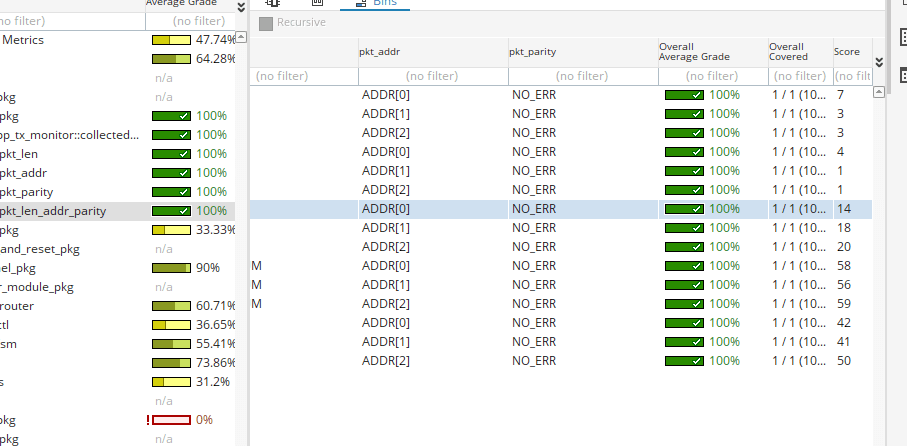

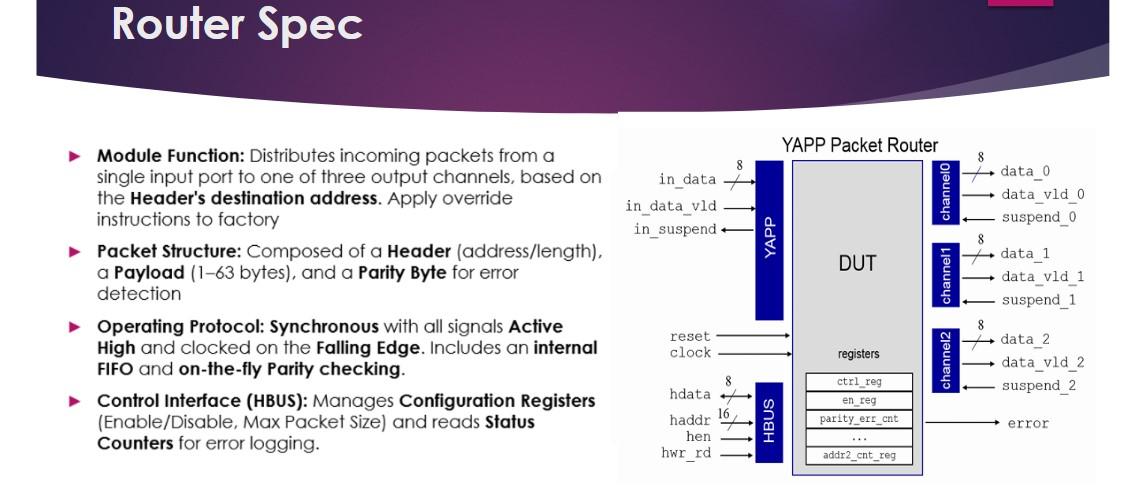

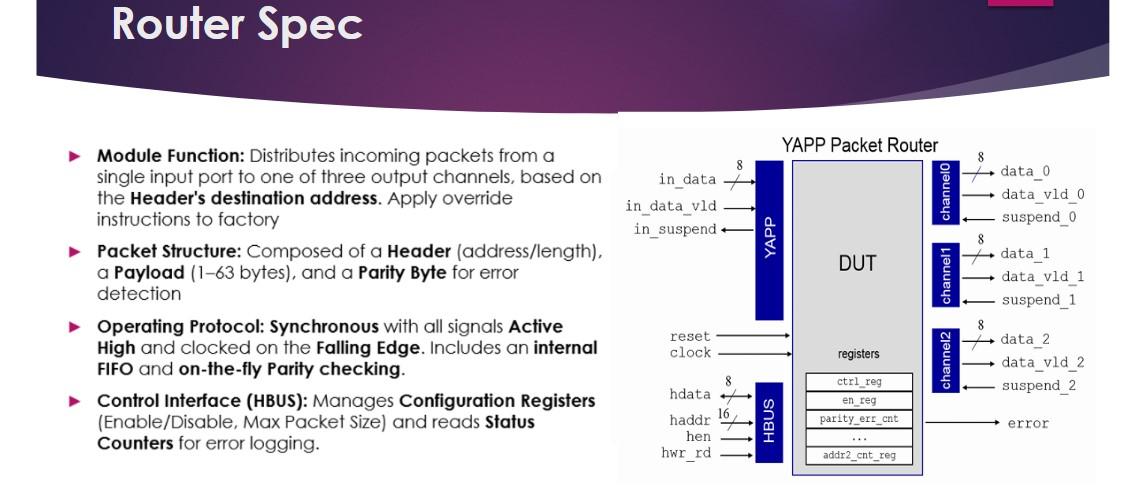

A full Universal Verification Methodology (UVM) testbench for verifying a hardware packet router. Includes YAPP, HBUS, and Channel UVCs; drivers, monitors, agents, virtual sequencers; reference model; scoreboard; RAL (Register Abstraction Layer); configuration database; objection handling; multiple directed and random sequences; multi-channel coordination; coverage plan; and register tests. Environment tests routing correctness, illegal packet handling, parity errors, invalid addresses, oversized packets, multi-channel concurrency, register access, and system-level integration.

Team Members

Cohort: Verification Bootcamp 2025 (Verification)

Responsibilities:

Developed a complete UVM-based verification environment for the YAPP Router, including transaction modeling, driver, sequencer, monitor, and agent, fully aligned with the packet protocol and router specification.

Designed a comprehensive library of UVM sequences, from basic packet flows to full system-level tests, verifying routing behavior across all channels, varying packet sizes, illegal addresses, and parity error scenarios.

Integrated the DUT using Virtual Interfaces and combined multiple UVCs—YAPP, HBUS, Channels, and Clock/Reset—into a unified, synchronized verification environment supporting full end-to-end system testing.

Implemented a modular Scoreboard and Reference Model using UVM TLM analysis ports to compare expected vs. actual packet routing, detect drops and errors, and provide detailed end-of-test reporting.

Developed functional coverage models capturing key routing scenarios, including combinations of address, packet length, parity conditions, and drop behavior, ensuring thorough and measurable verification completeness.

Modeled the router’s control and status registers using UVM RAL, executed read/write operations via HBUS sequences, and validated register values against DUT behavior and Scoreboard results.

...and more contributions not listed here

Responsibilities:

Integration of Multiple UVCs into a Unified Verification Environment Executed a full integration of the YAPP Input UVC, three Channel UVCs, the HBUS UVC, and the Clock & Reset UVC. Used the UVM Configuration Database, virtual interfaces, and TLM connectivity to assemble a cohesive, synchronized verification environment.

Development of a Coordinated Multichannel Sequencer Designed and implemented a multichannel sequencer that orchestrates operation between the YAPP and HBUS sequencers, enabling advanced test scenarios and tightly aligned multi-interface behavior.

Implementation of a Router Reference Model Based on HBUS Register Activity Built a reference model that reflects the DUT’s functionality by tracking updates from HBUS register writes, validating packet parameters (address, size, enable settings), and forwarding only compliant packets for scoreboard evaluation.

Construction of a TLM-Driven Scoreboard for Cross-Channel Packet Validation Created a scoreboard leveraging TLM analysis ports, per-channel FIFO structures, packet cloning, and tailored comparison mechanisms to verify packet correctness across all output channels of the router.

Authoring System-Level Test Sequences for Comprehensive Router Verification Developed complex test sequences combining YAPP traffic with HBUS configuration operations, including enabling/disabling router functionality, directing packets to multiple destinations, and verifying proper error responses to invalid addresses, oversize packets, and parity violations.

...and more contributions not listed here

Responsibilities:

Designed and implemented a full UVM verification environment for a multi-channel YAPP router, including agents, drivers, monitors, sequencers, and configuration objects.

Defined the verification strategy and vPlan, with aligned test scenarios, coverage goals, and feature traceability.

Developed a complete RAL model with frontdoor/backdoor access, register mirroring, prediction, and HBUS integration.

Built a cycle-accurate reference model and TLM-based scoreboard to validate routing correctness, packet integrity, errors, and protocol compliance across all channels.

Created constrained-random and directed sequences for packet traffic and register configuration, including system-level and corner-case scenarios.

Implemented comprehensive functional coverage for packet formats, routing behavior, register accesses, resets, and error conditions.

...and more contributions not listed here

Responsibilities:

Designed and implemented a complete UVM-based verification environment Built a full system-level UVM environment for the YAPP Router, integrating YAPP Input, three Channel UVCs, HBUS UVC, and Clock & Reset UVC using virtual interfaces, UVM configuration database, and TLM connectivity.

Defined the verification plan (vPlan) and test objectives Authored the verification plan outlining features to verify, test scenarios, coverage goals, and alignment between tests, coverage, and design requirements.

Developed an active YAPP agent and transaction flow Implemented an active YAPP agent including sequencer, driver, and monitor, with protocol-aware transaction modeling for packet generation, driving, and observation.

Implemented a virtual / multichannel sequencer Designed a virtual sequencer to coordinate stimulus between YAPP traffic and HBUS register configuration, enabling synchronized system-level test execution.

Built a reference model driven by HBUS register configuration Developed a reference model that mirrors router behavior based on HBUS register writes, validating packet legality (destination address, packet size, router enable state) before generating expected results.

Developed a TLM-based scoreboard for end-to-end verification Created a scoreboard using TLM analysis ports and per-channel queues to compare expected versus actual packets across all output channels, detecting routing errors, drops, and mismatches.

Authored system-level sequences and implemented functional coverage Developed directed and randomized sequences covering valid and invalid traffic scenarios, including illegal addresses, oversized packets, parity errors, and router enable/disable behavior. Implemented functional coverage for packet attributes, routing behavior, and cross scenarios to measure verification completeness.

...and more contributions not listed here

Responsibilities:

Built a robust, modular UVM environment for YAPP Router, fully implementing packet protocol with transactions, drivers, sequencers, monitors, and Agents.

Developed sequences of varying complexity to validate routing across all channels, different packet sizes, invalid addresses, and parity error conditions.

Seamlessly integrated multiple UVCs (YAPP, HBUS, Channels, Clock/Reset) to enable synchronized, full-system verification.

Developed a TLM Scoreboard and reference model for precise comparison of expected vs. actual outputs, monitoring drops and errors.

Designed functional coverage to ensure all critical routing scenarios were exercised, including combinations of addresses, packet lengths, parity, and drops.

Modeled control and counter registers with UVM RAL, executed read/write operations via HBUS, and verified register behavior against the reference model.

...and more contributions not listed here

Responsibilities:

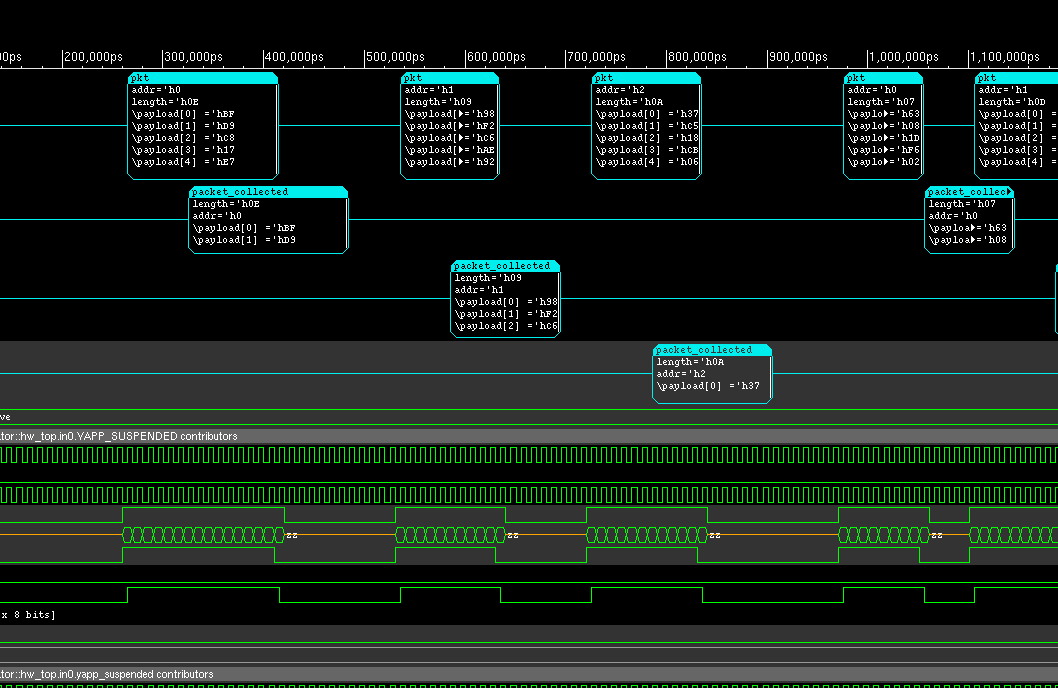

Executed full-system simulations, performed transaction tracing, analyzed waveform behavior, debugged constraints, and validated the correctness of the integrated verification environment.

Created the transaction-level stimulus model and implemented a sequence library generating constrained and protocol-accurate packet traffic.

Integrated all verification components with the DUT using virtual interfaces, including clock/reset logic, the YAPP input port, the HBUS interface, and output channels.

Combined multiple UVCs into a unified environment and coordinated multi-interface activity through a dedicated multichannel sequencer.

Implemented a TLM-based scoreboard that compares expected and actual packet routing across all DUT channels.

Developed a reference model that mirrors configuration settings and validates packet legality before forwarding them for end-to-end checking.

Performed full simulation runs, transaction tracing, and debugging to verify the correctness and stability of the integrated environment.

...and more contributions not listed here

Responsibilities:

Designed and implemented a complete UVM verification environment for a multi-channel YAPP Router, including agents, monitors, drivers, sequencers, and configuration objects.

Developed a full register model (RAL), including frontdoor/backdoor accesses, mirror & predict mechanisms, and integrated it into the testbench with a dedicated register sequencer and adapter.

Implemented a multi-channel sequencer and coordinated parallel traffic generation across multiple router interfaces, including constrained-random and directed sequences.

Built a functional scoreboard with a cycle-accurate reference model using TLM analysis FIFOs to check routing correctness, packet integrity, and protocol compliance.

Created comprehensive functional coverage for packet structure, routing behavior, state transitions, error cases, and register operations; aligned coverage items with the vPlan.

Wrote a detailed vPlan including assumptions, verification features, test scenarios, coverage goals, and expected DUT behaviors; maintained traceability between vPlan features and coverage.

Research: Performance improvement with multithreaded packet generation and scoreboard parallelization.

...and more contributions not listed here

Responsibilities:

Yapp Agent: I developed the YAPP agent as an active UVM component that injects randomized packets into the DUT, utilizing a sequencer, driver, and monitor to generate, drive, and observe stimuli for router verification.

Sequencer, Sequences, and Virtual Sequencer: I created yapp tx sequencer (extends uvm sequencer) to send packets to the driver with objection handling. I built sequences like yapp rnd seq, yapp bad addr_seq, yapp bad parity seq, yapp repeat addr seq, and yapp oversized seq for testing scenarios. I added a virtual sequencer to coordinate YAPP and HBUS stimuli for multichannel ops, skipping passive UVCs.

scoreboard: I implemented the scoreboard with a reference model that filters and forwards only valid packets—based on address, size, and router enable status—to queues for comparison against actual channel outputs, ensuring data integrity and error detection.

coverage: I designed the coverage model to verify comprehensive scenarios, including all destination addresses (0-3), various packet sizes (min, max, small, medium, large), parity modes, router enable states, and cross-coverage between addresses, sizes, and parity, along with reset and error conditions.

RAL: I modeled the DUT's registers and memories using the Register Abstraction Layer (RAL) for read/write access via the HBUS UVC, enabling frontdoor and backdoor operations to verify register functionality and synchronization with packet processing in tests like regaccesstest and regfunctiontest.

...and more contributions not listed here

Responsibilities:

Defined the complete verification strategy for the YAPP Router, including the verification plan, feature list, test categories, and bring-up stages. Established functional coverage goals and mapped every design requirement to a dedicated test or checker to ensure full specification alignment.

Developed protocol-accurate drivers for YAPP, CHANNEL, and HBUS interfaces, handling packet serialization, flow control, and register transactions. Implemented monitors that reconstruct packets and transactions, verify protocol correctness, and forward data to the reference model through analysis ports.

Built a cycle-accurate reference model that mirrors the router’s functional behavior, including routing logic, packet validation, parity checking, counter increments, error handling, and register modeling. The model maintains expected output queues and provides predicted results for scoreboard comparison.

Implemented a comprehensive scoreboard validating DUT behavior against the reference model. Added checkers for routing correctness, packet drops, error assertions, counter updates, memory storage validation, and register read/write accuracy. Ensured robust comparison across all channels and operational modes.

Implemented the full UVM environment components for the YAPP Router, including agents, drivers, monitors, sequencers, reference model, and scoreboard. Designed clean and modular interfaces (YAPP, CHANNEL, HBUS) and configured agent operation modes (ACTIVE/PASSIVE, Master/Slave) per test configuration.

Developed constrained-random sequences for YAPP packets, CHANNEL behavior, and HBUS transactions. Stimulus included varying packet lengths, addresses, parity conditions, error conditions, suspend behavior, and configuration operations to fully stress the design under both normal and corner-case scenarios.

Defined functional coverage for all design features, including packet types, address values, length ranges, parity modes, register accesses, suspend behavior, reset scenarios, and error events. Ensured cross-coverage between parity, address, enable bits, and packet size to confirm complete scenario exploration.

...and more contributions not listed here

B

No preview image

Responsibilities:

Established the UVM verification environment, including the top-level testbench, interfaces, and DUT connectivity.

Developed a full YAPP Agent consisting of a Driver, Monitor, and Sequencer following UVM principles.

Implemented a set of Sequences covering basic flows, randomized scenarios, and various traffic patterns.

Built a functional Reference Model that emulates the router behavior and serves as a golden reference.

Developed a Scoreboard that compares expected packets with observed packets to identify mismatches.

Added Functional Coverage groups to measure verification completeness across channels, IDs, and packet sizes.

Performed load and multi-channel stress tests to evaluate router behavior under high-traffic conditions.

...and more contributions not listed here

Responsibilities:

Integration of Multiple UVCs into a Unified Verification Environment Implemented full integration of the YAPP Input UVC, three Channel UVCs, the HBUS UVC, and the Clock & Reset UVC using UVM Configuration Database, Virtual Interfaces, and TLM connections to create a complete and synchronized verification environment.

Development of a Multichannel Sequencer for Coordinated Test Execution Designed and implemented a multichannel sequencer to coordinate activity between the YAPP Sequencer and the HBUS Sequencer, enabling complex test scenarios and synchronized multi-interface operations.

Implementation of a Router Reference Model Driven by HBUS Register Updates Developed a reference model that mirrors DUT behavior by tracking HBUS register writes, validating packet legality (address, size, enable state), and forwarding only valid packets for further scoreboard analysis.

Construction of a TLM-Based Scoreboard for Multi-Channel Packet Verification Built a scoreboard using TLM analysis imports, per-channel queues, packet cloning, and custom comparison logic to validate end-to-end packet correctness across all router output channels.

Creation of System-Level Test Sequences for Full Router Behavior Validation Authored advanced test sequences that combine YAPP and HBUS operations, including register configuration, enabling/disabling the router, sending packets to multiple addresses, and verifying error handling for illegal address, oversize packets, and parity faults.

...and more contributions not listed here