← Back to Students

Malka R.

Bio

Detail-oriented and self-disciplined developer with strong analytical thinking, fast learning ability, and hands-on experience in SystemVerilog, UVM, functional coverage, SVA, and C/C++. Brings a structured, creative problem-solving approach suited for verification roles while remaining adaptable to embedded systems and backend development.

Skills

Verilog

SystemVerilog

UVM

Functional Coverage

SVA

Testbench Architecture

Cadence Xcelium

Bootcamp Project

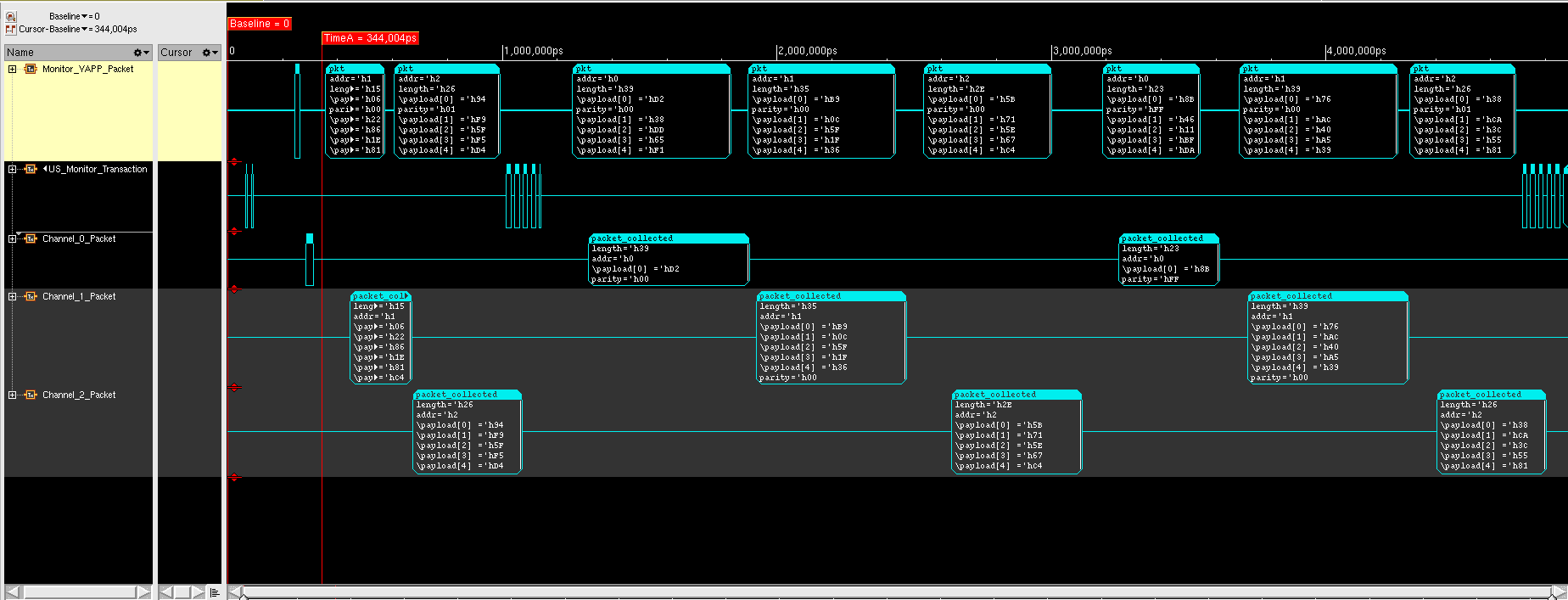

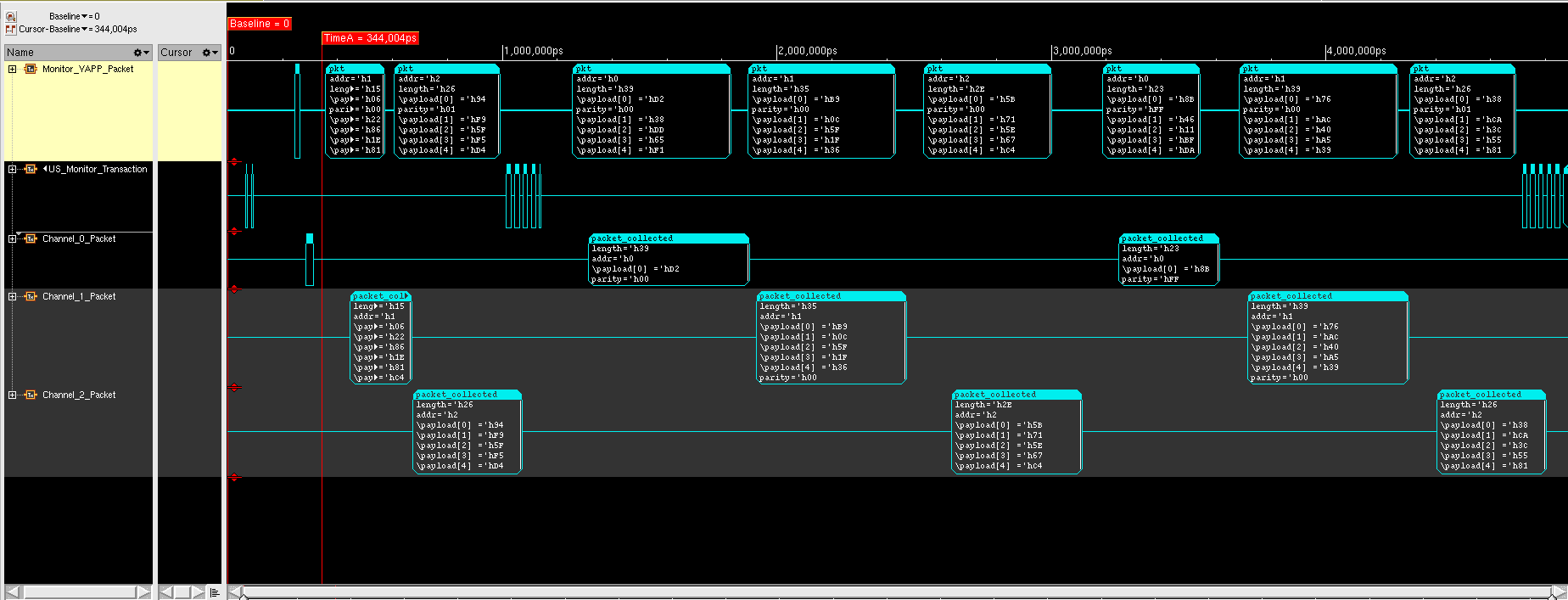

Complete UVM-based verification environment for a packet router

Mentored by: Qualcomm

Verification Bootcamp 2025 (Verification)

Responsibilities:

Defined the complete verification strategy for the YAPP Router, including the verification plan, feature list, test categories, and bring-up stages. Established functional coverage goals and mapped every design requirement to a dedicated test or checker to ensure full specification alignment.

Developed protocol-accurate drivers for YAPP, CHANNEL, and HBUS interfaces, handling packet serialization, flow control, and register transactions. Implemented monitors that reconstruct packets and transactions, verify protocol correctness, and forward data to the reference model through analysis ports.

Built a cycle-accurate reference model that mirrors the router’s functional behavior, including routing logic, packet validation, parity checking, counter increments, error handling, and register modeling. The model maintains expected output queues and provides predicted results for scoreboard comparison.

Implemented a comprehensive scoreboard validating DUT behavior against the reference model. Added checkers for routing correctness, packet drops, error assertions, counter updates, memory storage validation, and register read/write accuracy. Ensured robust comparison across all channels and operational modes.

Implemented the full UVM environment components for the YAPP Router, including agents, drivers, monitors, sequencers, reference model, and scoreboard. Designed clean and modular interfaces (YAPP, CHANNEL, HBUS) and configured agent operation modes (ACTIVE/PASSIVE, Master/Slave) per test configuration.

Developed constrained-random sequences for YAPP packets, CHANNEL behavior, and HBUS transactions. Stimulus included varying packet lengths, addresses, parity conditions, error conditions, suspend behavior, and configuration operations to fully stress the design under both normal and corner-case scenarios.

Defined functional coverage for all design features, including packet types, address values, length ranges, parity modes, register accesses, suspend behavior, reset scenarios, and error events. Ensured cross-coverage between parity, address, enable bits, and packet size to confirm complete scenario exploration.

Click to enlarge

Additional Projects

.End-to-end application combining a React client and a Node.js REST API backend.

Client: product catalog, cart, login, and admin dashboard.

Backend: authentication, product management, cart logic, and order processing.

English Level

Working Proficiency