← Back to Students

Chaya Z.

Bio

Analytical and detail-oriented developer, quick to learn new technologies and adapt to dynamic environments.

Skills

Verilog

SystemVerilog

UVM

Xcelium

Bootcamp Project

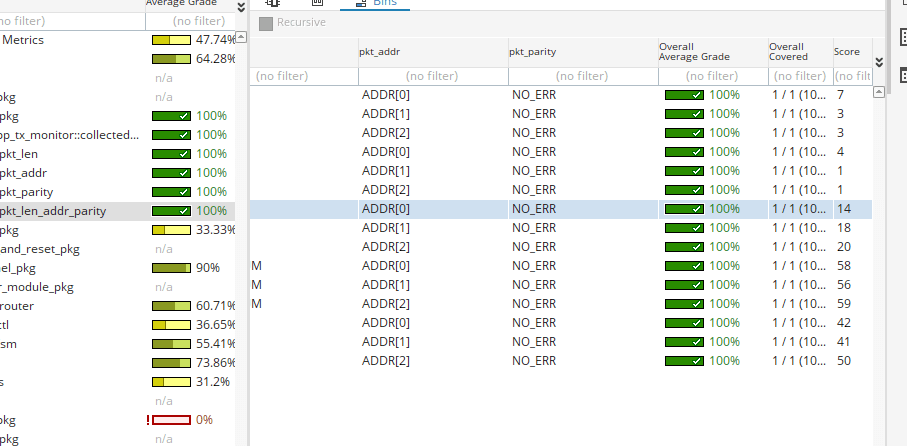

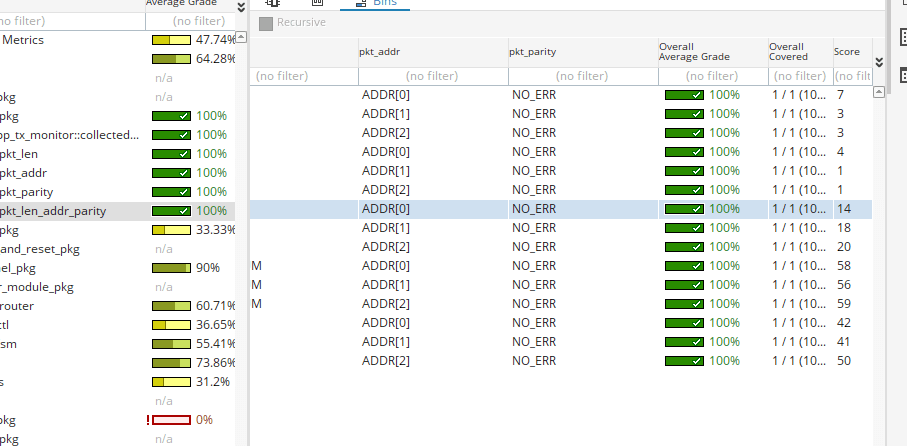

Complete UVM-based verification environment for a packet router

Mentored by: Qualcomm

Verification Bootcamp 2025 (Verification)

Responsibilities:

Integration of Multiple UVCs into a Unified Verification Environment Implemented full integration of the YAPP Input UVC, three Channel UVCs, the HBUS UVC, and the Clock & Reset UVC using UVM Configuration Database, Virtual Interfaces, and TLM connections to create a complete and synchronized verification environment.

Development of a Multichannel Sequencer for Coordinated Test Execution Designed and implemented a multichannel sequencer to coordinate activity between the YAPP Sequencer and the HBUS Sequencer, enabling complex test scenarios and synchronized multi-interface operations.

Implementation of a Router Reference Model Driven by HBUS Register Updates Developed a reference model that mirrors DUT behavior by tracking HBUS register writes, validating packet legality (address, size, enable state), and forwarding only valid packets for further scoreboard analysis.

Construction of a TLM-Based Scoreboard for Multi-Channel Packet Verification Built a scoreboard using TLM analysis imports, per-channel queues, packet cloning, and custom comparison logic to validate end-to-end packet correctness across all router output channels.

Creation of System-Level Test Sequences for Full Router Behavior Validation Authored advanced test sequences that combine YAPP and HBUS operations, including register configuration, enabling/disabling the router, sending packets to multiple addresses, and verifying error handling for illegal address, oversize packets, and parity faults.

Click to enlarge

Additional Projects

APB - protocol Verification Project — Technical Summary

In this project, a complete UVM UVC for the AMBA-APB protocol was developed from scratch. The work included creating a structured UVC package, implementing an APB interface aligned with the official specification, and defining all protocol signals together with dedicated modports for Master, Slave, and Monitor roles. An APB transaction item was designed to model the essential fields of each transfer—address, data, and command direction—while the driver handled all protocol control signals according to the standard Setup and Access phases. A basic sequence was implemented to generate both single and multi-item APB transfers using randomization and constraints. The Agent was fully constructed, including separate Master and Slave drivers, a sequencer, and a protocol-accurate monitor. Finally, the UVC was integrated into a testbench containing a provided APB Slave module, enabling verification of read/write operations and waveform analysis during simulation.

English Level

Working Proficiency