← Back to Students

Yaffi Y.

Bio

Highly analytical software developer with strong learning capabilities, deep technological understanding, and solid engineering-oriented thinking. Experienced in end-to-end system development, solving complex problems.

Skills

SystemVerilog

UVM

RTL Verification

Assertions

Coverage

Testbench

Cadence Xcelium

Bootcamp Project

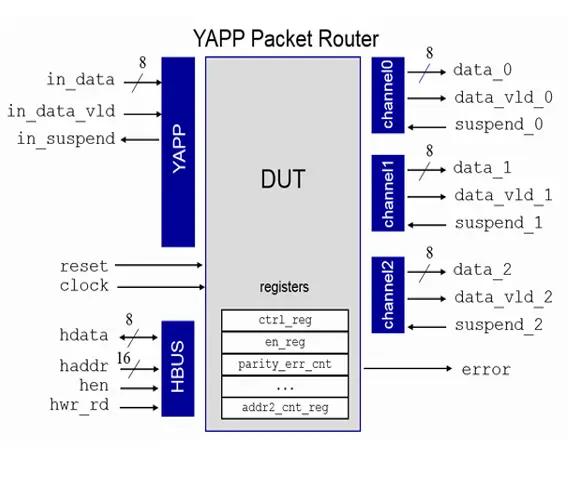

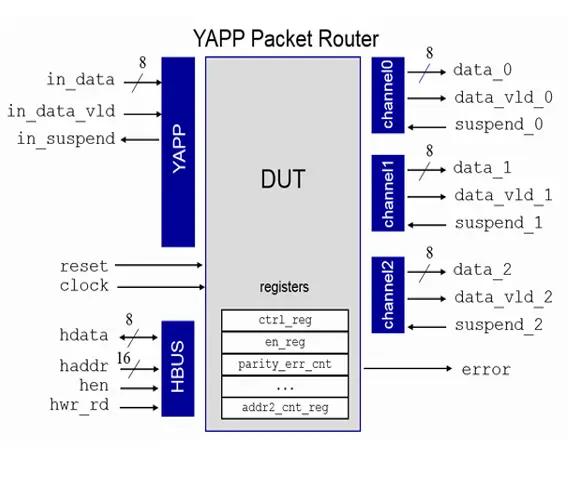

Complete UVM-based verification environment for a packet router

Mentored by: Qualcomm

Verification Bootcamp 2025 (Verification)

Responsibilities:

Designed and implemented a complete UVM verification environment for a multi-channel YAPP Router, including agents, monitors, drivers, sequencers, and configuration objects.

Developed a full register model (RAL), including frontdoor/backdoor accesses, mirror & predict mechanisms, and integrated it into the testbench with a dedicated register sequencer and adapter.

Implemented a multi-channel sequencer and coordinated parallel traffic generation across multiple router interfaces, including constrained-random and directed sequences.

Built a functional scoreboard with a cycle-accurate reference model using TLM analysis FIFOs to check routing correctness, packet integrity, and protocol compliance.

Created comprehensive functional coverage for packet structure, routing behavior, state transitions, error cases, and register operations; aligned coverage items with the vPlan.

Wrote a detailed vPlan including assumptions, verification features, test scenarios, coverage goals, and expected DUT behaviors; maintained traceability between vPlan features and coverage.

Research: Performance improvement with multithreaded packet generation and scoreboard parallelization.

Click to enlarge

Additional Projects

Full Stack: Appointment Scheduling System (React · .NET Core · SQL)

A complete system for managing appointments, treatments, and patient records for a clinic.

My part: Developed full React client including personal area and advanced filtering. Built backend Web API in .NET

Core with SQL database access and authorization logic. Implemented calendar management, treatment tracking, and administrator capabilities.

English Level

Fluent