← Back to Students

Shifra L.

Bio

Verification Engineering student with strong analytical skills, structured thinking, and deep system-level analysis abilities. Highly detail-oriented, reliable, and committed to high-quality verification standards. Quick learner with fast adaptation to new tools and technologies, bringing precise debugging capabilities and stable performance under pressure.

Skills

Verilog

SystemVerilog

UVM

RTL Verification

Virtual Sequencer

Scoreboard

RAL

Coverage

Testbench

Xcelium

Bootcamp Project

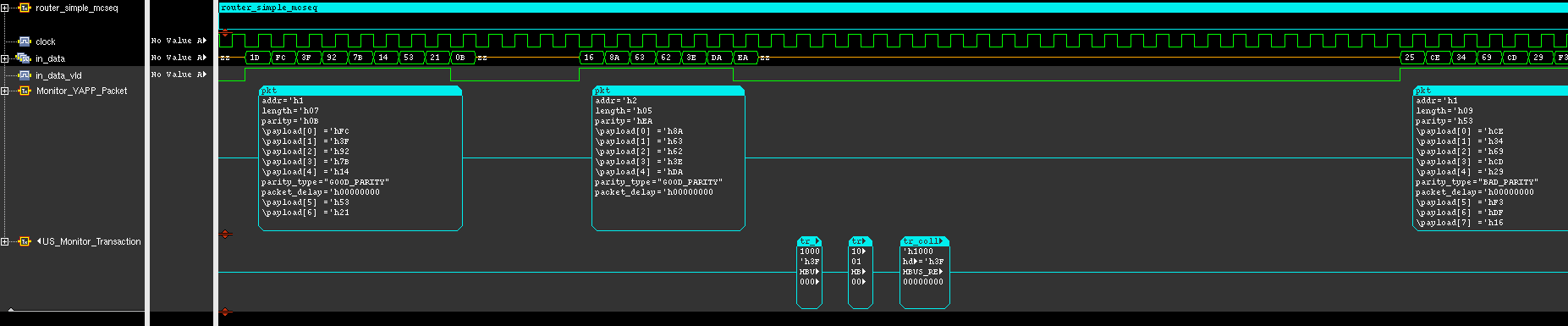

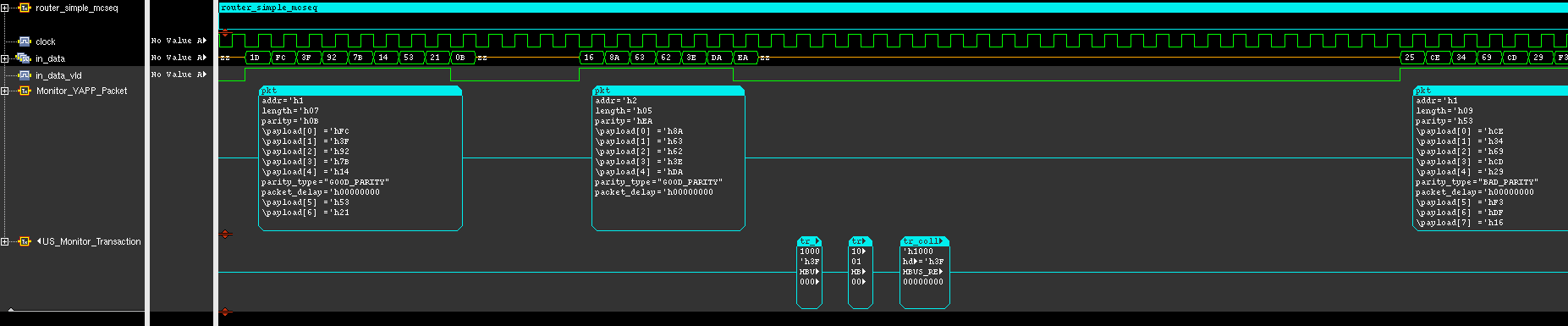

Complete UVM-based verification environment for a packet router

Mentored by: Qualcomm

Verification Bootcamp 2025 (Verification)

Responsibilities:

Yapp Agent: I developed the YAPP agent as an active UVM component that injects randomized packets into the DUT, utilizing a sequencer, driver, and monitor to generate, drive, and observe stimuli for router verification.

Sequencer, Sequences, and Virtual Sequencer: I created yapp tx sequencer (extends uvm sequencer) to send packets to the driver with objection handling. I built sequences like yapp rnd seq, yapp bad addr_seq, yapp bad parity seq, yapp repeat addr seq, and yapp oversized seq for testing scenarios. I added a virtual sequencer to coordinate YAPP and HBUS stimuli for multichannel ops, skipping passive UVCs.

scoreboard: I implemented the scoreboard with a reference model that filters and forwards only valid packets—based on address, size, and router enable status—to queues for comparison against actual channel outputs, ensuring data integrity and error detection.

coverage: I designed the coverage model to verify comprehensive scenarios, including all destination addresses (0-3), various packet sizes (min, max, small, medium, large), parity modes, router enable states, and cross-coverage between addresses, sizes, and parity, along with reset and error conditions.

RAL: I modeled the DUT's registers and memories using the Register Abstraction Layer (RAL) for read/write access via the HBUS UVC, enabling frontdoor and backdoor operations to verify register functionality and synchronization with packet processing in tests like regaccesstest and regfunctiontest.

Click to enlarge

Additional Projects

In VeriRISC CPU project, I designed and verified the Memory module for managing CPU data, including internal storage array and core Write (data insertion) and Read (data retrieval) operations.

The parametric Verilog module defines DWIDTH for data width and AWIDTH for address width, with inputs clk, wr, rd, addr, and bidirectional data port; it performs writes to memory if wr=1 and reads to output if rd=1 on rising clock edges, defaulting to High-Z otherwise.

In SystemVerilog, I created a testbench with dedicated Writemem and Readmem tasks for basic tests like reset and sequential data sending, added random stimuli (e.g., constrained ASCII characters or 80/20 upper/lower letters), incorporated interfaces and virtual interfaces for modular testing, randomization classes for diverse inputs, coverage points for addresses/input/output validation, and dynamic/associative arrays plus queues for delayed data checks, all simulated in SimVision and Cadence IMC to ensure 100% functionality.

English Level

Working Proficiency