← Back to Students

Neomi A.

Bio

Detail-driven verification engineer with a solid software development background and strong analytical thinking. Quick, independent learner with practical experience gained in the Qualcomm–KamaTech intensive program and through personal Embedded and Full-Stack projects. Motivated by complex technical challenges and enthusiastic about designing efficient, high-quality solutions.

Skills

Python

C++

C

Node.js

.NET

React

TypeScript

PostgreSQL

Docker

WebSockets

SystemVerilog

UVM

RTL Verification

Assertions

Coverage

Testbench

Cadence Xcelium

Bootcamp Project

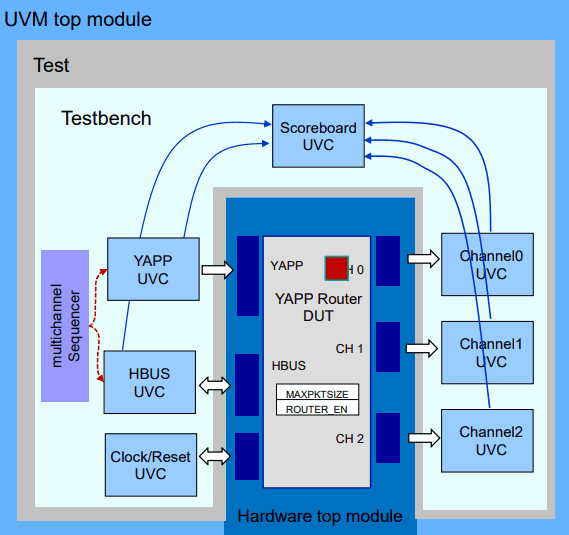

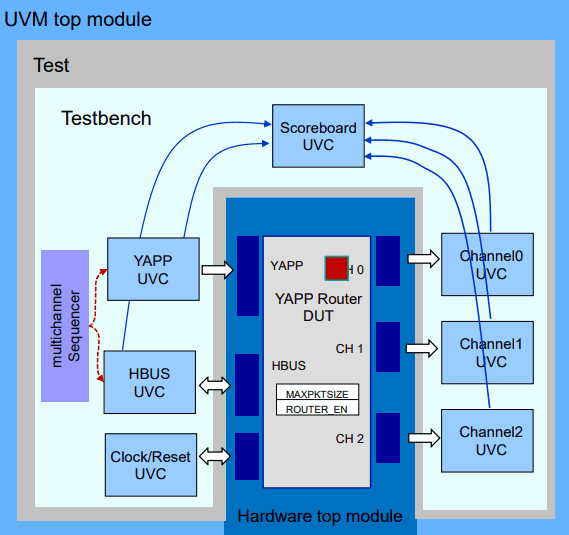

Complete UVM-based verification environment for a packet router

Mentored by: Qualcomm

Verification Bootcamp 2025 (Verification)

Responsibilities:

Integration of Multiple UVCs into a Unified Verification Environment Executed a full integration of the YAPP Input UVC, three Channel UVCs, the HBUS UVC, and the Clock & Reset UVC. Used the UVM Configuration Database, virtual interfaces, and TLM connectivity to assemble a cohesive, synchronized verification environment.

Development of a Coordinated Multichannel Sequencer Designed and implemented a multichannel sequencer that orchestrates operation between the YAPP and HBUS sequencers, enabling advanced test scenarios and tightly aligned multi-interface behavior.

Implementation of a Router Reference Model Based on HBUS Register Activity Built a reference model that reflects the DUT’s functionality by tracking updates from HBUS register writes, validating packet parameters (address, size, enable settings), and forwarding only compliant packets for scoreboard evaluation.

Construction of a TLM-Driven Scoreboard for Cross-Channel Packet Validation Created a scoreboard leveraging TLM analysis ports, per-channel FIFO structures, packet cloning, and tailored comparison mechanisms to verify packet correctness across all output channels of the router.

Authoring System-Level Test Sequences for Comprehensive Router Verification Developed complex test sequences combining YAPP traffic with HBUS configuration operations, including enabling/disabling router functionality, directing packets to multiple destinations, and verifying proper error responses to invalid addresses, oversize packets, and parity violations.

Click to enlarge

Additional Projects

✦ APB Protocol Verification

This project involved developing a full UVM UVC for the AMBA-APB protocol entirely from the ground up. The work included building a well-organized UVC package, implementing a protocol-compliant APB interface, and defining all required signals with dedicated modports tailored for Master, Slave, and Monitor components.

A custom APB transaction class was created to encapsulate key transfer attributes—address, data, and read/write direction. The driver was responsible for driving all control signals precisely according to the Setup and Access phases defined in the AMBA specification.

A basic sequence was implemented to produce randomized APB traffic, supporting both single and burst-style transfers via constrained randomization.

The Agent was fully assembled, including individual Master and Slave drivers, a sequencer, and a monitor capable of capturing and reporting protocol-accurate behavior.

Finally, the UVC was integrated into a testbench environment containing a provided APB Slave DUT, enabling execution of read/write scenarios, functional checking, and waveform examination throughout simulation.

English Level

Fluent