← Back to Students

Yael E.

Bio

High self-learning ability | High ownership & work ethic | Analytical thinking

Skills

SystemVerilog

UVM

RTL Verification

Assertions

Coverage

Testbench

Cadence Xcelium

Bootcamp Project

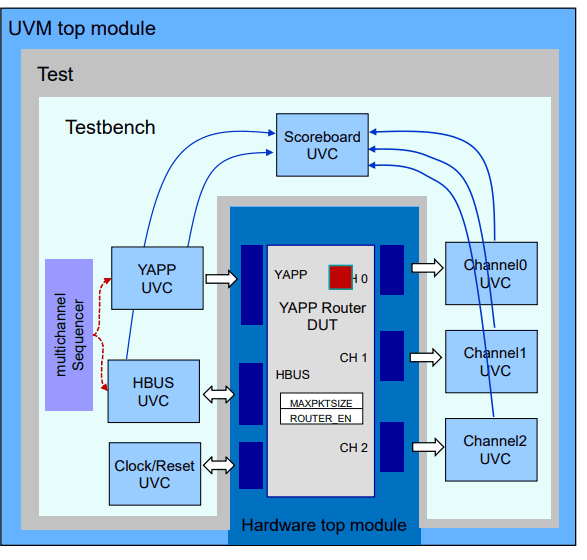

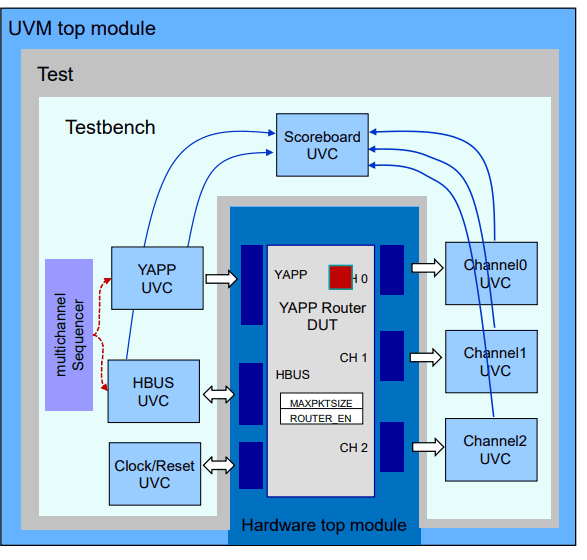

Complete UVM-based verification environment for a packet router

Mentored by: Qualcomm

Verification Bootcamp 2025 (Verification)

Responsibilities:

Built a robust, modular UVM environment for YAPP Router, fully implementing packet protocol with transactions, drivers, sequencers, monitors, and Agents.

Developed sequences of varying complexity to validate routing across all channels, different packet sizes, invalid addresses, and parity error conditions.

Seamlessly integrated multiple UVCs (YAPP, HBUS, Channels, Clock/Reset) to enable synchronized, full-system verification.

Developed a TLM Scoreboard and reference model for precise comparison of expected vs. actual outputs, monitoring drops and errors.

Designed functional coverage to ensure all critical routing scenarios were exercised, including combinations of addresses, packet lengths, parity, and drops.

Modeled control and counter registers with UVM RAL, executed read/write operations via HBUS, and verified register behavior against the reference model.

Click to enlarge

Additional Projects

Exam Scheduling Tool – Full-stack C# & React application with SQL Server backend that automatically schedules exams without student conflicts using a graph-coloring algorithm.

English Level

Fluent